Understanding and Resolving "Invalid Map K T Key" Errors in Vivado

Related Articles: Understanding and Resolving "Invalid Map K T Key" Errors in Vivado

Introduction

In this auspicious occasion, we are delighted to delve into the intriguing topic related to Understanding and Resolving "Invalid Map K T Key" Errors in Vivado. Let’s weave interesting information and offer fresh perspectives to the readers.

Table of Content

Understanding and Resolving "Invalid Map K T Key" Errors in Vivado

In the realm of FPGA design, Vivado, Xilinx’s powerful design suite, plays a crucial role in translating high-level descriptions of circuits into the intricate configurations required for actual hardware implementation. During this process, known as synthesis and implementation, a variety of errors can arise, one of which is the perplexing "invalid map k t key" message. This error, often encountered during the mapping stage of the implementation flow, signifies a discrepancy between the design’s intended behavior and the capabilities of the targeted FPGA device.

This article aims to provide a comprehensive understanding of this error, its root causes, and strategies for resolving it effectively. By dissecting the error message and exploring its implications, we aim to empower FPGA designers to navigate this common obstacle and achieve successful hardware implementations.

Decoding the Error: Unveiling the "K T Key" Mystery

The "invalid map k t key" error message indicates that Vivado has encountered a constraint or a design element that is incompatible with the specific mapping capabilities of the targeted FPGA device. To understand this error, we need to delve into the concepts of "K" and "T" keys, which are fundamental to the mapping process.

- K Key: The "K" key represents the key used to identify a specific location or resource within the FPGA device. This key is unique for every individual resource, such as a lookup table (LUT), flip-flop, or memory block.

- T Key: The "T key," on the other hand, refers to the type of resource being utilized. It specifies the characteristics of the resource, such as the size of the LUT, the type of flip-flop, or the memory configuration.

During the mapping stage, Vivado attempts to match the design elements, such as logic gates, registers, and memory blocks, to available resources on the FPGA device. This matching process relies on the "K" and "T" keys. If Vivado encounters a mismatch, it cannot effectively map the design element, resulting in the "invalid map k t key" error.

Common Causes of the "Invalid Map K T Key" Error

Several factors can contribute to the occurrence of this error:

-

Mismatched Constraints: The most prevalent cause is the use of constraints that conflict with the actual capabilities of the target FPGA device. These constraints can include:

- Incorrectly specified resource types: Assigning a specific resource type that is unavailable on the target device.

- Conflicting placement constraints: Specifying placement constraints that are incompatible with the physical layout of the device.

- Unrealistic timing constraints: Setting timing constraints that are too stringent or unrealistic for the target device.

- Design Complexity: Complex designs with intricate logic structures and numerous interconnections can increase the likelihood of encountering mapping issues.

- Device Specific Limitations: Each FPGA device has its own unique architecture and resource limitations. Using a resource that is not supported by the chosen device can lead to the "invalid map k t key" error.

- Design Bugs: Logic errors or design inconsistencies can also contribute to mapping difficulties, resulting in the error message.

Strategies for Resolving the "Invalid Map K T Key" Error

Addressing the "invalid map k t key" error involves a systematic approach that focuses on identifying and rectifying the underlying cause. Here’s a step-by-step guide:

-

Review Constraints: Carefully examine the constraints applied to the design. Ensure that they are accurate, realistic, and compatible with the target FPGA device. Pay particular attention to:

- Resource Type Constraints: Verify that the specified resource types are available on the target device. Consult the device datasheet or documentation for a complete list of supported resources.

- Placement Constraints: Check for any conflicting placement constraints that might hinder the mapping process. Consider relaxing or removing unnecessary placement constraints.

- Timing Constraints: Analyze the timing constraints and ensure they are achievable within the limitations of the target device.

- Analyze Design Complexity: Evaluate the complexity of the design. Consider breaking down large and complex designs into smaller, more manageable modules. This can simplify the mapping process and reduce the likelihood of errors.

- Utilize Device Specific Features: Familiarize yourself with the specific features and limitations of the chosen FPGA device. Leverage its unique capabilities to optimize the design for efficient mapping.

- Debugging and Verification: Employ debugging techniques to identify and resolve any logic errors or design inconsistencies that might contribute to mapping problems. Utilize simulation and formal verification tools to ensure the correctness of the design.

- Consult Vivado Documentation: Refer to the Vivado documentation for detailed information on mapping procedures, constraints, and device-specific features. The documentation provides valuable insights into best practices and troubleshooting techniques.

FAQs: Addressing Common Queries

Q: Can I ignore the "invalid map k t key" error?

A: Ignoring this error is not recommended. It indicates a fundamental incompatibility between the design and the target device, which can lead to unpredictable behavior, incorrect functionality, and potential performance degradation.

Q: How can I determine the specific "K" and "T" keys causing the error?

A: The Vivado logs and reports often provide detailed information about the specific "K" and "T" keys involved in the error. Examine the error messages and reports carefully to identify the problematic resources.

Q: What are some common mistakes that lead to this error?

A: Common mistakes include:

- Using outdated device libraries: Ensure you are using the latest device libraries compatible with the target FPGA.

- Misinterpreting device specifications: Carefully read the device datasheet and documentation to understand the supported resources and limitations.

- Over-constraining the design: Avoid overly restrictive constraints that might hinder the mapping process.

Q: Can I use a different FPGA device to avoid this error?

A: Choosing a different FPGA device with a different architecture and resource set might resolve the error. However, it’s crucial to ensure that the chosen device meets the design requirements and specifications.

Tips for Preventing Future "Invalid Map K T Key" Errors

- Prioritize Design Planning: Carefully plan the design, considering the target FPGA device and its capabilities from the outset.

- Use Constraints Effectively: Apply constraints judiciously, ensuring they are accurate, realistic, and compatible with the target device.

- Leverage Device-Specific Features: Explore the unique features and capabilities of the chosen FPGA device to optimize the design for efficient mapping.

- Employ Comprehensive Verification: Utilize simulation and formal verification tools to thoroughly test and verify the design before implementation.

- Stay Updated with Vivado Documentation: Regularly consult the Vivado documentation for the latest best practices, troubleshooting techniques, and device-specific information.

Conclusion

The "invalid map k t key" error, while seemingly cryptic, is a valuable indicator of a mismatch between the design and the targeted FPGA device. Understanding the underlying causes of this error and adopting a systematic approach to resolve it is crucial for achieving successful FPGA implementations. By carefully reviewing constraints, analyzing design complexity, and leveraging device-specific features, designers can navigate this common obstacle and achieve efficient and reliable hardware implementations. Remember, a well-planned and meticulously verified design, combined with a thorough understanding of FPGA architecture and mapping processes, is the key to avoiding this error and achieving successful FPGA development.

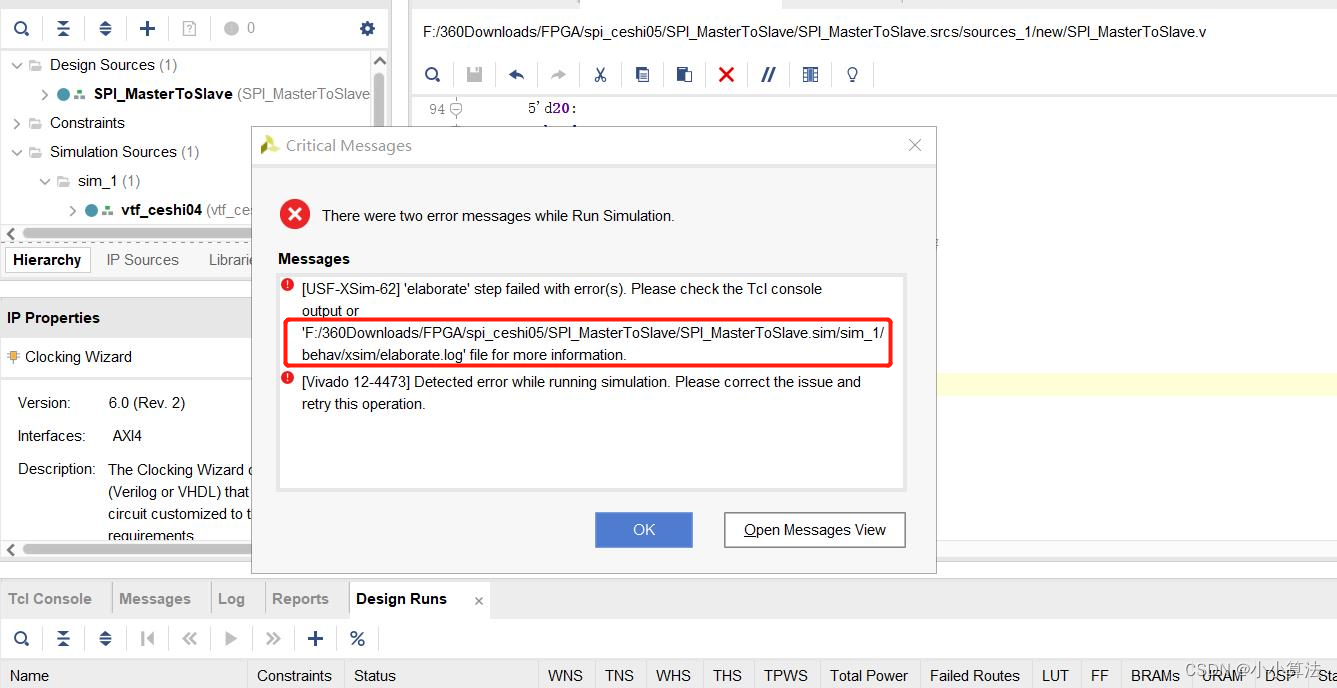

![vivado报错-ERROR: [Common 17-39] ‘program_hw_devices‘ failed due to earlier errors_program hw](https://img-blog.csdnimg.cn/5c790cc6ea154a1882767347db86cc14.png)

Closure

Thus, we hope this article has provided valuable insights into Understanding and Resolving "Invalid Map K T Key" Errors in Vivado. We appreciate your attention to our article. See you in our next article!